## **T1-DS1/E1-CEPT Framer Formatter**

## Description

The 29C96 is a programmable CMOS device interfacing with T1-DS1 or E1-CEPT transceivers. The 29C96 supports following frame formats :

• DS1 : 4 frames (DMI), D4 (G704), ESF (G704), SLC-96 (DMI), DDS (DMI)

• CEPT : double frame, CRC4

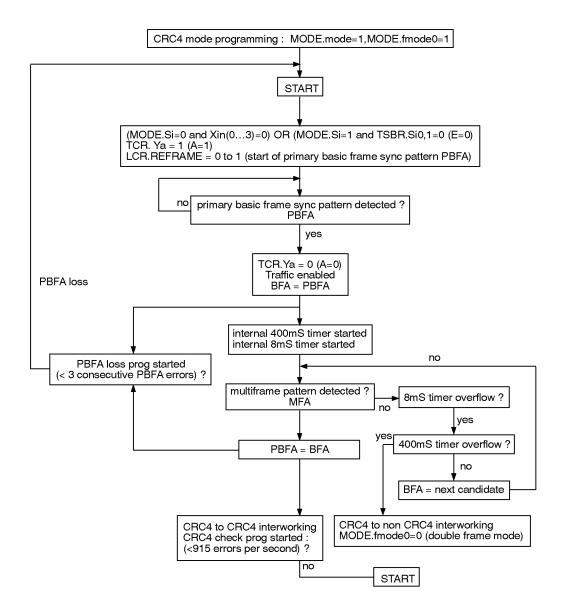

In CEPT mode the modified CRC4 multiframe alignment algorithm of G706 (Appendix B) recommendation is supported in order to allow interworking of equipments with and without CRC4 capability.

Line coding is ZCS (zero suppression mode), B8ZS (T1) or HDB3 (E1). Several signalling modes are supported by the 29C96 :

- DS1 : Transparent 0 to 16 states robbed bit signalling mode or Common Channel signalling (channel 24 CCS) mode.

- CEPT : Transparent, IRSM or Channel associated mode.

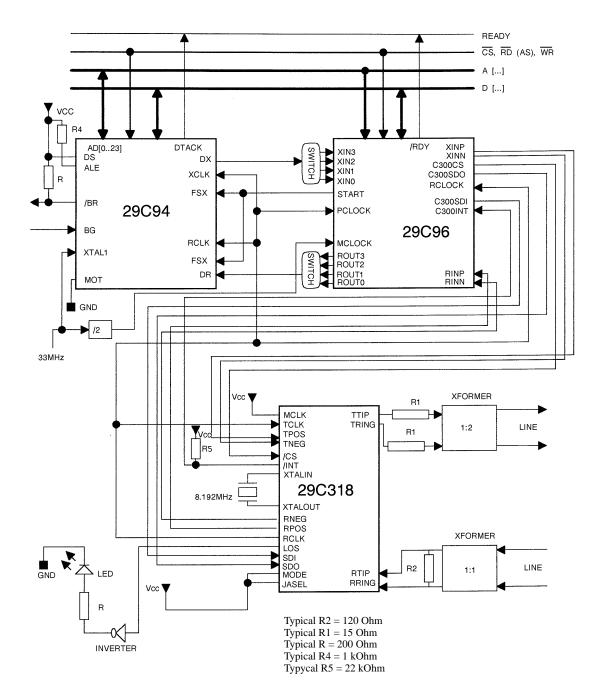

• Signalling source can be external (input pin) or internal (signalling RAM). The 29C96 allows CLEAR CHANNEL capability in DS1 for mixed voice and data channels. The 29C96 synchronizer/formatter handles alarm generation and detection, error detection and counting, and performance monitoring. The host

microprocessor controls operations of the 29C96 via the 8 bit data bus/7 bit address bus by reading the internal addressable registers or via an interrupt sequence. The 29C96 offers line control capability with a variety of LOOP BACK modes. Monitoring of B8ZS/HDB3, out of frame and CRC errors can be programmed through registers and control lines. The 29C96 handles different types of alarms (YELLOW alarm, BLUE alarm and multiframe alarm). The system interface includes independant serial in/out ports for signalling data and data-link, associated with a variety of Frame, Superframe, signalling and Data-link synchronization signals. The 29C96 can interface up to four PCM buses or 1 to 128 time slots. The 29C96 can transfer T1 or CEPT frames to a 24 or 32 time slots bus with the dedicated clocks. Each incoming or outgoing data from T1/E1 frame can be written or read at any time slot of any PCM bus. All unselected PCM time slots are put in high-Z mode. Each incoming data from frame can be replaced by a programmable MASK code. Each outgoing data from PCM can be replaced by a programmable IDLE code, by the AIS (ALARM INDICATION SIGNAL) code, patched with signalling data or form a CLEAR CHANNEL (transparent transmission). Programming of the 29C3xx transceiver is done through a dedicated '29C3xx port.'

## Features

- TI/CEPT compatible frame formatter

- AMI or inverted AMI encoding with selectable "0" suppression mode :

- B8ZS (T1 DS1)

- HDB3 (E1 CEPT)

- ZCS

- Supports common and individual signalling modes in T1 and E1 modes.

- Supports the following modes for T1 DS1 :

- 4 frames (193N),

- D4,

- DDS,

- ESF,

- SLC-96

- Supports the following modes for E1 CEPT :

- Double frame

- CRC4 (Modified CRC4 alignment algorithm in G706 supported),

## Applications

- Computer to PBX interfaces (DMI)

- T1/E1 digital trunk interfaces

- Digital cross-connect interfaces

- High speed computer to computer data links

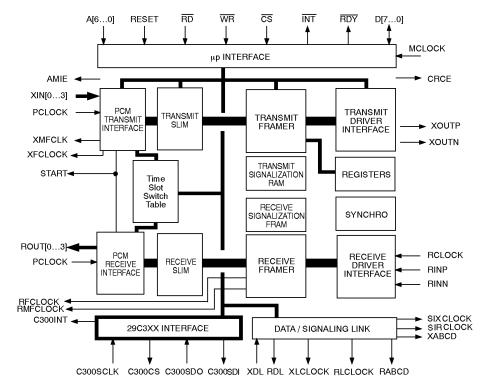

## **Functional Block Diagram**

## Description

## **PCM Interface**

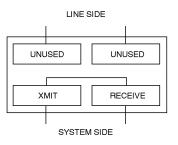

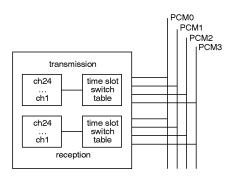

Transmit/receive PCM block is in charge of data transfer between the SLIM memory and PCM interface. This interface includes  $4 \times$  programmable serial bus (E1 or T1), it can be connected to 29C94 HDLC controller or to 29C95 ECMA102 controller. It includes :

-  $4 \times$  parallel/serial (PISO) adaptators for receiver

- $4 \times \text{serial/parallel}$  (SIPO) adaptators for transmitter

- $1 \times 128 \times 8$  buffer for receiver

- $1 \times 128 \times 8$  buffer for transmitter

- 1 finite state machine used to transfer data between SIPOs and  $128 \times 8$  buffer.

## **SLIM Memory**

The SLIM memory is interfacing between FRAMER and PCM interface. Both receiver and transmitter include a  $[32 \times 8] \times 2$  SLIM RAM. This memory is in charge of network clock jitter absorbtion.

## Framer

Framer is interfacing between SLIM memory and DRIVER interface. It is in charge of data/F/signalization framing and unframing. In case of internal programming, all signalization data is read/written from/to 2 internal 32  $\times$  8 banks.

## **Driver Interface Block**

This block is interfacing between the FRAMER and DRIVER interface. It can be connected to 29C3xx driver and it is in charge of :

- data encoding/decoding (B8ZS/HDB3/ZCS),

- CRC calculation/checking

## 29C3xx Interface

This block is in charge of 29C3xx programmation through a dedicated interface (see 29C3xx datasheet). It includes a parallel/serial adaptor and hardware logic in

# TEMIC MATRA MHS

order to control the 29C3xx in Host Mode Operation (CLKE).

## **Data Link/signalling Block**

This block is in charge of interfacing between data link/external signalling source and FRAMER. It includes :

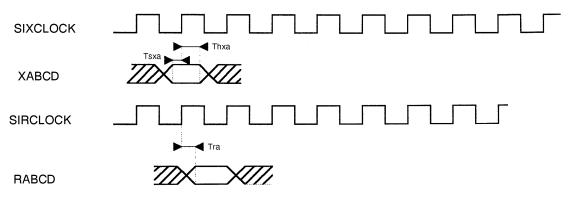

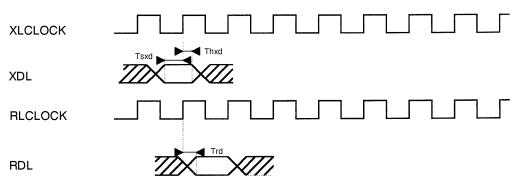

- clock generation (XLCLOCK, SIXCLOCK, RLCLOCK, SIRCLOCK),

- serial/parallel adaptation

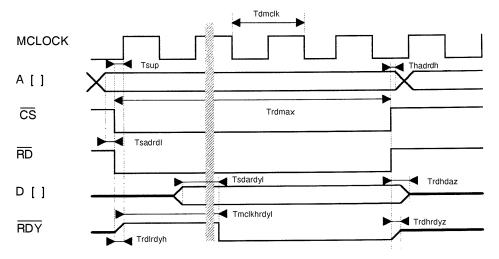

## μ**P Interface**

This block is in charge of interfacing various microprocessors through an 8-bit data bus and a 7-bit address bus.

## **Time Slot Switch Registers**

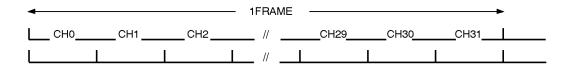

The total number of time slots/channels handled at PCM

interface is 128. The TSSR is in charge of channel assignation between the PCM interface and the FRAMER, the 29C96 can only process 32 time slots in E1 mode and 24 time slots in T1 mode.

## **Signalization RAM**

The SIGNALIZATION RAM is a  $2 \times 32 \times 8$  RAM on both side providing/storing signalization data to/from the FRAMER when the Internal signalization source mode is programmed.

## Synchro Block

This block is in charge of circuit synchronization using frame and multiframe signalling.

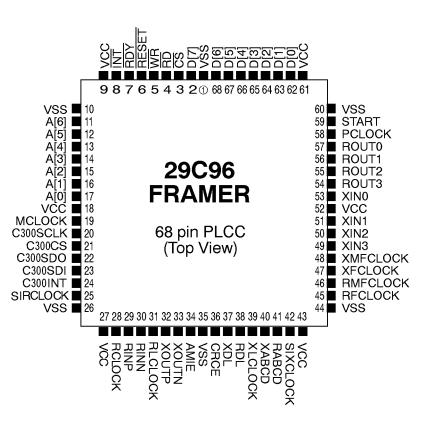

## Pinout

# **29C96**

# ΤΕΜΙΟ

## MATRA MHS

| PIN           | NAME     | ТҮРЕ   | DESCRIPTION                                                                                                                                                                             |

|---------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VSS      | SUPPLY | GROUND                                                                                                                                                                                  |

| 2,6268        | D[7:0]   | I/O    | 8 bit microprocessor data bus (Bi-directional).                                                                                                                                         |

| 3             | CS       | I      | Chip-select (active low) : selects the 29C96 addressing and allows data transfer through D0-D7 data bus.                                                                                |

| 4             | RD       | Ι      | READ (active low) : enables data transfer from 29C96 to D0-D7 data bus.                                                                                                                 |

| 5             | WR       | Ι      | WRITE (active low) : enables data transfer from D0-D7 data bus to 29C96.                                                                                                                |

| 6             | RESET    | Ι      | Active low, a '0' applied on this pin initializes registers to a reset value (see § 2).                                                                                                 |

| 7             | RDY      | 0      | READY : a high to low transition on this pin indicates that the 29C96 is ready to transfer in-<br>formation to/from the data bus. When the 29C96 is not selected, this pin is floating. |

| 8             | ĪNT      | 0      | INTERRUPT REQUEST. When low, this pin indicates that the 29C96 is requesting an interrupt to the host microprocessor.                                                                   |

| 9             | VCC      | SUPPLY | 5 V ± 10 % Supply                                                                                                                                                                       |

| 10            | VSS      | SUPPLY | Ground                                                                                                                                                                                  |

| 11<br>-<br>17 | A[6:0]   | I      | 7 bit address bus.                                                                                                                                                                      |

| 18            | VCC      | SUPPLY | 5 V ± 10 % Supply                                                                                                                                                                       |

| 19            | MCLOCK   | I      | Microprocessor clock.<br>Minimum frequency 10 MHz.                                                                                                                                      |

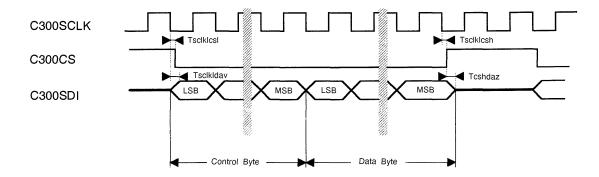

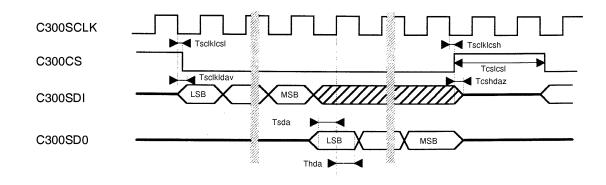

| 20            | C300SCLK | 0      | 29C300 interface serial clock must be connected to pin 27 of 29C3xx primary rate transceiver.                                                                                           |

| 21            | C300CS   | 0      | 29C300 interface chip select must be connected to pin 26 of 29C3xx primary rate transceiver.                                                                                            |

| 22            | C300SDO  | I      | 29C300 interface serial data out must be connected to pin 25 of 29C3xx primary rate transceiver.                                                                                        |

| 23            | C300SDI  | 0      | 29C300 interface serial data in must be connected to pin 24 of 29C3xx primary rate transceiver.                                                                                         |

| 24            | C300INT  | Ι      | 29C300 interface interrupt request must be connected to pin 23 of 29C3xx primary rate trans-<br>ceiver.                                                                                 |

| 25            | SIRCLOCK | 0      | Signalling receive clock.                                                                                                                                                               |

| 26            | VSS      | SUPPLY | Ground.                                                                                                                                                                                 |

| 27            | VCC      | SUPPLY | 5 V ± 10 % Supply.                                                                                                                                                                      |

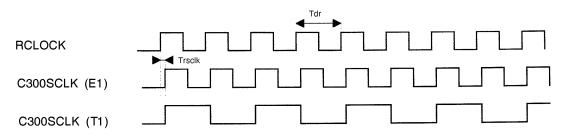

| 28            | RCLOCK   | Ι      | Receive line clock : 1.544 MHz primary clock (T1)/2.048 MHz primary clock (E1).                                                                                                         |

| 29            | RINP     | Ι      | AMI positive receive data input.                                                                                                                                                        |

| 30            | RINN     | Ι      | AMI negative receive data input.                                                                                                                                                        |

| 31            | RLCLOCK  | 0      | Signalling clock output.                                                                                                                                                                |

| 32            | XOUTP    | 0      | AMI positive transmit data output.                                                                                                                                                      |

| 33            | XOUTN    | 0      | AMI negative transmit data output.                                                                                                                                                      |

| 34            | AMIE     | 0      | Multifunction pin. AMIE = 1 indicates an AMI error when this mode is selected.                                                                                                          |

| 35            | VSS      | SUPPLY | Ground.                                                                                                                                                                                 |

| 36            | CRCE     | 0      | CRCE = 1 indicates a CRC error in ESF or CRC4 modes.                                                                                                                                    |

| 37            | XDL      | I      | Transmit data link input for FDL bit in ESF mode and D bits in DDS.SLC, IRSM modes.                                                                                                     |

# ΤΕΜΙΟ

MATRA MHS

| PIN | NAME     | ТҮРЕ   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 38  | RDL      | 0      | Receive data link output for FDL bits in ESF mode and D bits in DDS, SLC, IRSM modes.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 39  | XLCLOCK  | 0      | Data link transmit clock for XDL.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 40  | XABCD    | Ι      | Transmit signalling data input (data input for ABCD signalling bits).                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 41  | RABCD    | 0      | Receive signalling data output (data output for ABCD signalling bits).                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 42  | SIXCLOCK | 0      | Transmit signalling clock for XABCD.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 43  | VCC      | SUPPLY | 5 V ± 10 % Supply.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 44  | VSS      | SUPPLY | Ground.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

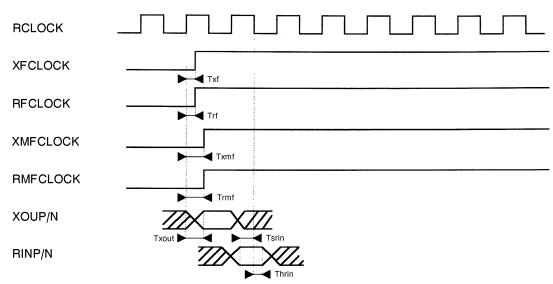

| 45  | RFCLOCK  | 0      | Receive frame synchronization pulse. A low to high transition occurs with the first bit of a frame. Period of this pulse is $125 \ \mu$ s. Duration of high level is one time slot.                                                                                                                                                                                       |  |  |  |  |

| 46  | RMFCLOCK | 0      | Receive multiframe synchronization pulse. A low to high transition occurs with the first bit of a multiframe and high to low transition occurs on the first bit of the second frame. Period of this pulse is 1.5 ms (D4), 3.0 ms (ESF), 6.0 ms (SLC), 250 $\mu$ s (DOUBLEFRAME) or 2 ms (CRC4). Duration of high level is 125 $\mu$ s.                                    |  |  |  |  |

| 47  | XFCLOCK  | 0      | Transmit frame synchronization pulse. A low to high transition occurs with the first bit of a frame. Period of this pulse is $125 \ \mu$ s. Duration of high level is one time slot.                                                                                                                                                                                      |  |  |  |  |

| 48  | XMFCLOCK | 0      | Transmit multiframe synchronization pulse. A low to high transition occurs with the first bit of a multiframe and is active during the first frame, high to low transition occurs on the first bit of the second frame. Period of this pulse is 1.5 ms (D4), 3.0 ms (ESF), 6.0 ms (SLC), 250 $\mu$ s (DOUBLEFRAME) or 2 ms (CRC4). Duration of high level is 125 $\mu$ s. |  |  |  |  |

| 49  | XIN3     | Ι      | PCM3 transmit data input.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 50  | XIN2     | Ι      | PCM2 transmit data input.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 51  | XIN1     | Ι      | PCM1 transmit data input.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 52  | VCC      | SUPPLY | 5 V ± 10 % Supply.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 53  | XIN0     | Ι      | PCM0 transmit data input.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 54  | ROUT3    | 0      | PCM3 receive data output.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 55  | ROUT2    | 0      | PCM2 receive data output.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 56  | ROUT1    | 0      | PCM1 receive data output.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 57  | ROUT0    | 0      | PCM0 receive data output.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

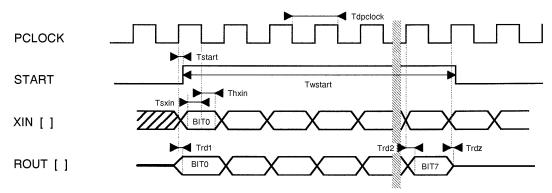

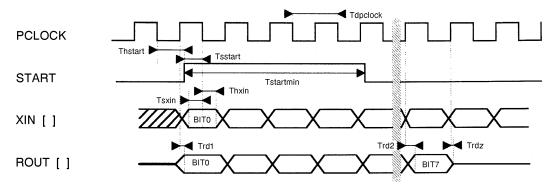

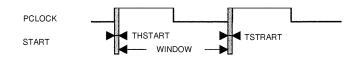

| 58  | PCLOCK   | I      | PCM0, 1, 2, 3 transmit/receive interface clock : 1.544 MHz (T1) or 2.048 MHz (E1). This clock can be doubled (3.088/4.096 MHz) or multiplied by 4 (6.196/8.192 MHz).                                                                                                                                                                                                      |  |  |  |  |

| 59  | START    | I/O    | PCM transmit synchronization start pulse.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 60  | VSS      | SUPPLY | Ground.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 61  | VCC      | SUPPLY | 5 V ± 10 % Supply.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

## Registers

## 1. Register Mapping

| R/W | : | Read and Write register. | T/C | : | Register exists in T1 and E1. |

|-----|---|--------------------------|-----|---|-------------------------------|

| R   | : | Read only register.      | С   | : | Register exists in E1 only.   |

| W   | : | Write only register.     | Т   | : | Register exists in T1 only.   |

| ADDRESS MODE DESCRIPTION |       |        |        | DECONTRACT                          |      |

|--------------------------|-------|--------|--------|-------------------------------------|------|

| NAME                     | HEX   | DEC    | - MODE | DESCRIPTION                         | TYPE |

| ALARM                    | 00    | 0      | T/C    | ALARM REGISTER                      | R    |

| ERROR                    | 01    | 1      | T/C    | ERROR REGISTER                      | R    |

| MSR                      | 02    | 2      | T/C    | MEMORY STATUS REGISTER              | R    |

| SSR                      | 03    | 3      | T/C    | SYNCHRONIZATION STATUS REGISTER     | R    |

| TCR                      | 04    | 4      | T/C    | TRANSMIT CONTROL REGISTER           | R/W  |

| MODE                     | 05    | 5      | T/C    | MODE REGISTER                       | R/W  |

| LSCR                     | 06    | 6      | T/C    | LOOPBACK and SIGNALLING REGISTER    | R/W  |

| LCR                      | 07    | 7      | T/C    | LINE CONTROL REGISTER               | R/W  |

| FCR                      | 08    | 8      | T/C    | FRAMER CONTROL REGISTER             | R/W  |

| MASK0                    | 09    | 9      | T/C    | MASK REGISTER 0                     | R/W  |

| MASK1                    | 0A    | 10     | T/C    | MASK REGISTER 1                     | R/W  |

| MASK2                    | 0B    | 11     | T/C    | MASK REGISTER 2                     | R/W  |

| TDLR or                  | 0C    | 12     | Т      | TRANSMIT DATA LINK REGISTER (T1)    | R/W  |

| TSBR                     |       |        | C      | TRANSMIT SPARE BITS REGISTER (CEPT) | R/W  |

| RDLR or                  | 0D    | 13     | Т      | RECEIVE DATA LINK REGISTER (T1)     | R/W  |

| RSBR                     |       |        | C      | RECEIVE SPARE BITS REGISTER (CEPT)  | R/W  |

| IDLE                     | 0E    | 14     | T/C    | IDLE REGISTER                       | R/W  |

| ICR0                     | 0F    | 15     | T/C    | IDLE CHANNELS REGISTER 0            | R/W  |

| ICR1                     | 10    | 16     | T/C    | IDLE CHANNELS REGISTER 1            | R/W  |

| ICR2                     | 11    | 17     | T/C    | IDLE CHANNELS REGISTER 2            | R/W  |

| ICR3                     | 12    | 18     | T/C    | IDLE CHANNELS REGISTER 3            | R/W  |

| RMR                      | 13    | 19     | T/C    | RECEIVE MASK REGISTER               | R/W  |

| MCR0                     | 14    | 20     | T/C    | MASK CHANNELS REGISTER 0            | R/W  |

| MCR1                     | 15    | 21     | T/C    | MASK CHANNELS REGISTER 1            | R/W  |

| MCR2                     | 16    | 22     | T/C    | MASK CHANNELS REGISTER 2            | R/W  |

| MCR3                     | 17    | 23     | T/C    | MASK CHANNELS REGISTER 3            | R/W  |

| CLAR                     | 18    | 24     | T/C    | CHANNEL LOOPBACK ADDRESS REGISTER   | R/W  |

| XBR                      | 19    | 25     | C      | EXTRA BITS REGISTER                 | R/W  |

| PMR                      | 1A    | 26     | T/C    | PCM MODE REGISTER                   | R/W  |

| CCR0                     | 1B    | 27     | Т      | CLEAR CHANNEL REGISTER 0            | R/W  |

| CCR1                     | 1C    | 28     | Т      | CLEAR CHANNEL REGISTER 1            | R/W  |

| CCR2                     | 1D    | 29     | Т      | CLEAR CHANNEL REGISTER 2            | R/W  |

| MXT                      | 1E    | 30     | T/C    | 29C300 REGISTER                     | R/W  |

| ASR                      | 1F    | 31     | T/C    | ALARM STATUS REGISTER               | R    |

| CEC0                     | 20    | 32     | T/C    | CRC ERROR COUNTER 0                 | R/W  |

| CEC1                     | 21    | 33     | T/C    | CRC ERROR COUNTER 1                 | R/W  |

| FEC0                     | 22    | 34     | T/C    | FRAMING BIT ERROR COUNTER 0         | R/W  |

| FEC1                     | 23    | 35     | T/C    | FRAMING BIT ERROR COUNTER 1         | R/W  |

| AEC0                     | 24    | 36     | T/C    | AMI ERROR COUNTER 0                 | R/W  |

| AEC1                     | 25    | 37     | T/C    | AMI ERROR COUNTER 1                 | R/W  |

| TSR132                   | 405F  | 6495   | T/C    | TRANSMIT SIGNALLING REGISTER 132    | W    |

| RSR132                   | 405F  | 6495   | T/C    | RECEIVE SIGNALLING REGISTER 132     | R    |

| TSSR132                  | 60.7F | 96.127 | T/C    | TIME SLOT SWITCHING REGISTER 132    | R/W  |

MATRA MHS

## 2. Registers Description

| 2.1 ALARM | I REGISTE                   | R ALARM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RESET = 0                          | @ = 00H R                         |              |                 |                                    |  |  |  |  |

|-----------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------|--------------|-----------------|------------------------------------|--|--|--|--|

| Ya        | FTEMPO                      | Ys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LFA                                | LMA                               | LSMA         | C300<br>BUSY    | C300<br>INT                        |  |  |  |  |

| bit 0     | 1                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                  | 4                                 | 5            | 6               | 7                                  |  |  |  |  |

| .Ya       | d<br>b                      | Ya=1 Upon detection of a REMOTE FRAME ALARM (YELLOW ALARM). Detection depends on framing mode (D4, ESF, SLC96, DOUBLE FRAME, CRC4). In E1 mode, this bit is also called A bit, it is used to signal RAI (Remote Alarm Indication), Ya = 1 upon detection of a RAI.                                                                                                                                                                                                                                                                                                                |                                    |                                   |              |                 |                                    |  |  |  |  |

| .FTEMPO   | r<br>ti<br>4<br>r<br>a<br>7 | In E1 mode this bit is used to signal the end of the 400 ms timer for CRC4 alignment research. This bit is set to one at the same time that CRC4 bit into SSR register to signal that the CRC4 alignment has not been found twice within 8 ms period at the end of the 400 ms timer. Depending on the values written into ALFA and ALMA bits (see LCR register), the 29C96 will jump into double frame mode or restart a new multiframe alignment.<br>T1 : If FTEMPO=1 and LCR.FORCE=1 and there is more than 1 candidate BFA will be locked to the next candidate automatically. |                                    |                                   |              |                 |                                    |  |  |  |  |

| .Ys       | У                           | s=1 upon dete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ction of a REM                     | 10TE MULTII                       | FRAME ALAR   | RM.             |                                    |  |  |  |  |

| .LFA      | r<br>E                      | eceived with er<br>E1 mode : Loss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ror status (Ft b<br>of frame align | oits in 4-frame/<br>ment, LFA=1 v | D4/SLC96, FA | S bits in ESF). | bits have been<br>gnment Signals   |  |  |  |  |

| .LMA      | C<br>v<br>4                 | in time slot 0 are received with error status.<br>Loss of Multiframe Alignment (E1, CRC4 mode). This bit is set to one when 915 over 1000<br>CRC4 multiframe patterns are received with error status. (T1 mode) This bit is set to one<br>when 2 out of 4 multiframing bits have been received with error status (Fs bits) or when<br>4 "channel 24" multiframe patterns are received with error status within 12 frames in DDS<br>format.                                                                                                                                        |                                    |                                   |              |                 |                                    |  |  |  |  |

| .LSMA     |                             | E1 mode (LSM<br>nultiframing pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |                                   |              | nent, LSMA=1    | when 2 CAS                         |  |  |  |  |

| .C300BUSY | S                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ite access to th                   | ne MXT registe                    |              |                 | is set to one to<br>unt and a read |  |  |  |  |

| .C300INT  | (                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |                                   |              |                 | en detected on<br>en loaded into   |  |  |  |  |

| AMIE                                                              | CAND           | XSMU                         | XSMO                                                                                        | AISD                                                                                                                                       | CRCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EBIT                                                                                                                                                                                                                                                                        | FAach                                                                                                                                                                                                                                                                    |  |  |

|-------------------------------------------------------------------|----------------|------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0                                                                 | 1              | 2                            | 3                                                                                           | 4                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                                                                                                                        |  |  |

|                                                                   |                |                              |                                                                                             |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                          |  |  |

| ND                                                                | Т              | 1 mode : CAN                 | D = 1 When the                                                                              | nere is no candi                                                                                                                           | date for synch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ronization.                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                          |  |  |

| .XSMU XSMU=1 When the slip memory detects an underflow condition. |                |                              |                                                                                             |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                          |  |  |

| MO                                                                | Х              | XSMO=1 When                  | n the slip memo                                                                             | ory detects an o                                                                                                                           | overflow condi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | tion.                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                          |  |  |

|                                                                   | 0<br>IIE<br>ND | 0 1<br>IIE A<br>ND T<br>MU X | 0     1     2       IIE     AMIE=1 Upon       ND     T1 mode : CAN       MU     XSMU=1 When | 0     1     2     3       IIE     AMIE=1 Upon detection of A       ND     T1 mode : CAND = 1 When the MU       XSMU=1 When the slip memory | 0     1     2     3     4       IIE     AMIE=1 Upon detection of AMI error.       ND     T1 mode : CAND = 1 When there is no candid       MU     XSMU=1 When the slip memory detects an upper sector and the slip memory detects and upper sector and the slip memory detects and upper sector and upper secto | 0       1       2       3       4       5         IIE       AMIE=1 Upon detection of AMI error.         ND       T1 mode : CAND = 1 When there is no candidate for synchmatic terror.         MU       XSMU=1 When the slip memory detects an underflow conditioned terror. | 0       1       2       3       4       5       6         IIE       AMIE=1 Upon detection of AMI error.         ND       T1 mode : CAND = 1 When there is no candidate for synchronization.         MU       XSMU=1 When the slip memory detects an underflow condition. |  |  |

## 2.2 ERROR REGISTER ERROR RESET = 0 @ = 01H R

.AISD This bit is set to one when an AIS is Detected. If the 29C96 receives successive AIS, this bit will be set to one during the reception of the first AIS.

| .CRCE  | This bit is set to one when the computed CRC4 or CRC6 does not match the received CRC4 or CRC6. In order to know in which submultiframe is located the error, see STATUS REGISTER.                 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .EBIT  | This bit is set to one when the E bit (also represented as Si bit) located in the frame number 13 or 15 is set to zero (indication of a bad CRC in one submultiframe coming from the remote side). |

| .FAach | This bit is set to one when the synchronization state machine has performed a <u>F</u> rame Alignement achievement i.e. when BFA or MFA has been set to one by the 29C96.                          |

| RSBR/RDLR                                                                                                                                            | TSBR/TDLR                                                                                                                                                   | EBRF           | XRACK            | SRF              | AEC              | CEC           | FEC       |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|------------------|---------------|-----------|--|--|--|

| bit 0                                                                                                                                                | 1                                                                                                                                                           | 2              | 3                | 4                | 5                | 6             | 7         |  |  |  |

| .RSBR/RDLRRSBR(E1) = 1 indicates that the Receive Spare Bit Register is full.<br>RDLR(T1) = 1 indicates that the Receive Data Link Register is full. |                                                                                                                                                             |                |                  |                  |                  |               |           |  |  |  |

| .TSBR/TDLR                                                                                                                                           | .TSBR/TDLRTSBR(E1) = 1 indicates that the Transmit Spare Bit Register is empty.<br>TDLR(T1) = 1 indicates that the Transmit Data Link Register is empty.    |                |                  |                  |                  |               |           |  |  |  |

| .EBRF                                                                                                                                                | EBRF E1 only : EBRF = 1 indicates that transmit and/or receive Extra Bit Register is empty<br>and/or full depending on bit3 and bit4 of Extra Bit Register. |                |                  |                  |                  |               |           |  |  |  |

| .XRACK                                                                                                                                               | У                                                                                                                                                           | KRACK = 1 wh   | nen transmit sig | gnalling RAM     | is ready to be u | pdated.       |           |  |  |  |

| .SRF                                                                                                                                                 | S                                                                                                                                                           | SRF = 1 when t | he content of r  | eceive signallir | ng RAM has be    | en completely | received. |  |  |  |

| .AEC                                                                                                                                                 | A                                                                                                                                                           | AEC = 1 when   | AMI error cou    | nter reaches the | e maximum cou    | unt.          |           |  |  |  |

| .CEC                                                                                                                                                 | (                                                                                                                                                           | CEC = 1 when   | CRC error cou    | nter reaches the | e maximum cou    | unt.          |           |  |  |  |

| .FEC                                                                                                                                                 | F                                                                                                                                                           | FEC=1 when FI  | RAMING error     | r counter reach  | es the maximum   | m count.      |           |  |  |  |

## 2.3 MEMORY STATUS REGISTER MSR RESET = 0 @ = 02H R

Only ALARM, ERROR, MEMORY STATUS registers generate an interrupt when a bit inside these three registers changes from 0 to 1. The interrupt will not be cleared until the register causing the interrupt has been read. It means that the **interrupt detection mecanism** of the host system must be **activated on the low level** of /INT pin.

#### 2.4 SYNCHRONIZATION STATUS REGISTER SSR RESET = 00 @=03H R

| SYNC  | BFA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MFA                                                                                                                                                                                                                                                                                                                                             | CRC4 | CRCE0 | CRCE1 | EBIT0 | EBIT1 |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|-------|-------|--|--|--|--|

| bit 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                               | 3    | 4     | 5     | 6     | 7     |  |  |  |  |

| SYNC  | This bit is set to one when a synchronization pattern is recognized in the received data frame (in E1 mode).                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                 |      |       |       |       |       |  |  |  |  |

| BFA   | This bit is set to one if the synchronization pattern is recognized in the frame n and the bit 2 of the frame $n + 1$ is correct and there is no synchronization pattern in this frame and the synchronization pattern will be also found into frame $n + 2$ .                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |      |       |       |       |       |  |  |  |  |

| MFA   | a<br>li                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (MultiFrame Alignment) : This bit is set to one when the multiframe alignment is realised<br>and the available CRC synchronization pattern is found at least twice within 8 ms in the<br>limit of 400 ms (according to G 706). At the end of this timer an automatic reframe can<br>be done if ALMA and ALFA (see LCR register) are set to one. |      |       |       |       |       |  |  |  |  |

|       | be done if ALMA and ALFA (see LCR register) are set to one.<br>After a reframe initialized by user (see LCR register : toggle on REFRAME bit) or by<br>ALMA/ALFA on FTEMPO event, these three bits (SYNC, BFA, MFA) are set to zero and<br>the research alignment procedure is started.<br>If at the end of the 8 ms period during the multiframe alignment research within the 400 ms<br>timer, the multiframe alignment pattern is not found twice, these three bits (SYNC, BFA,<br>MFA) will be reset to (1, 0, 0) when the reset cycle of 8 ms starts. |                                                                                                                                                                                                                                                                                                                                                 |      |       |       |       |       |  |  |  |  |

# ΤΕΜΙΟ

MATRA MHS

| CRC4         | This bit is set to one when the CRC4 alignment is not found in order to signal that the component has changed from CRC4 mode to double frame mode. This bit will stay high during all the time the component will be in double frame mode.                          |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CRCE0        | This bit is set to one when an erroneous CRC4/6 has been detected into the submultiframe 0 due to comparaison between received CRC4/6 and computed CRCR4/6. This information is duplicated on CRCE pin (pin 36) and its duration (on this output) will be 6 frames. |

| CRCE1        | This bit is set to one when an erroneous CRC4/6 has been detected into the submultiframe 1. This information is duplicated on CRCE pin (pin 36) and its duration will be 6 frames.                                                                                  |

| EBIT0, EBIT1 | These two bits are the copy of E bits located into the frame number 13 and 15 of the received multiframe.                                                                                                                                                           |

## 2.5 CRC ERROR COUNTER 0 and 1 CEC0/CEC1 RESET = 0 @=20H/21H R/W

| CEC0  |   |   |   |   |   |   |   |

|-------|---|---|---|---|---|---|---|

|       |   |   |   |   |   |   |   |

| CEC1  |   |   |   |   |   |   |   |

|       |   |   |   |   |   |   |   |

| bit 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

CEC0 : 8 bits register forming the lower byte of the 16 bits CRC error counter (CEC). CEC1 : 8 bits register forming the upper byte of the 16 bits CRC error counter (CEC).

## 2.6 FRAMING BIT ERROR COUNTER 0 and 1 FEC0/FEC1 RESET = 0 @=22H/23H R/W

| bit 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|-------|---|---|---|---|---|---|---|

|       |   |   |   |   |   |   |   |

| FEC1  |   |   |   |   |   |   |   |

|       |   |   |   |   |   |   |   |

| FEC0  |   |   |   |   |   |   |   |

FEC0 : 8 bits register forming the lower byte of the 16 bits Framing bits error counter (FEC). FEC1 : 8 bits register forming the upper byte of the 16 bits Framing bit error counter (FEC).

## 2.7 AMI ERROR COUNTER 0 and 1 AEC0/AEC1 RESET = 0 @=24H/25H R/W

AEC0

| AEC1  |   |   |   |   |   |   |   |

|-------|---|---|---|---|---|---|---|

|       |   |   |   |   |   |   |   |

| bit 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

AEC0 : 8 bits register forming the lower byte of the 16 bits AMI Error Counter (AEC). AEC1 : 8 bits register forming the upper byte of the 16 bit AMI Error Counter (AEC).

Concerning CEC0, CEC1, FEC0, FEC1, AEC0, AEC1 registers, a write loads the counter from which the mecanism counts down every time a corresponding error occurs. Each time one of the counters reaches 0000H, an interrupt occurs and the corresponding bit into MSR register is set to one (see AEC, CEC, FEC) and the counter will automatically restart from the original preset value.

**29C96**

| Ya         | AIS                        | SAIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Yam              | Ys                             | AYa                | AAIS          | AYS               |  |  |  |  |

|------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|--------------------|---------------|-------------------|--|--|--|--|

| bit 0      | 1                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                | 4                              | 5                  | 6             | 7                 |  |  |  |  |

| Ya         |                            | When this bit is<br>et to one in E1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | if AYa bit is no               | ot set to one, a c | continuous RA | I is sent (A bits |  |  |  |  |

| AIS        | V                          | When this bit is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | set to one, a fi | ramed all one's                | pattern is sent.   |               |                   |  |  |  |  |